## UA 880 D · UB 880 D · VB 880 D

8-Bit-Mikroprozessoren in n-Kanal-Silicon-Gate-Technologie (CPU)

158 Befehle umfassender Befehlssatz mit 16-, 8-, 4- und Einzel-Bit-Instruktion sowie zusätzliche Adressierweisen

(indizierte, relative und Bitadressierung)

- Taktfrequenz: UA 880 D = 4 MHz ( $\vartheta_a = 0 \dots 70^\circ\text{C}$ )

UB 880 D = 2,5 MHz ( $\vartheta_a = 0 \dots 70^\circ\text{C}$ )

VB 880 D = 2,5 MHz ( $\vartheta_a = -25 \dots 85^\circ\text{C}$ )

- 3 schnelle Interrupt-Behandlungsarten und ein zusätzlicher, nicht maskenprogrammierbarer Interrupt

- 21 interne Register

- Einphasentakt und nur eine Betriebsspannung von 5 V

- direkter Anschluß von dynamischen und statischen Standardspeicherchips ohne zusätzlichen Bauelementeaufwand möglich

- integrierte dynamische Refresh-Hardware

- die Eingänge sind voll TTL-kompatibel, die Ausgänge können eine Standard-TTL-Last treiben

---

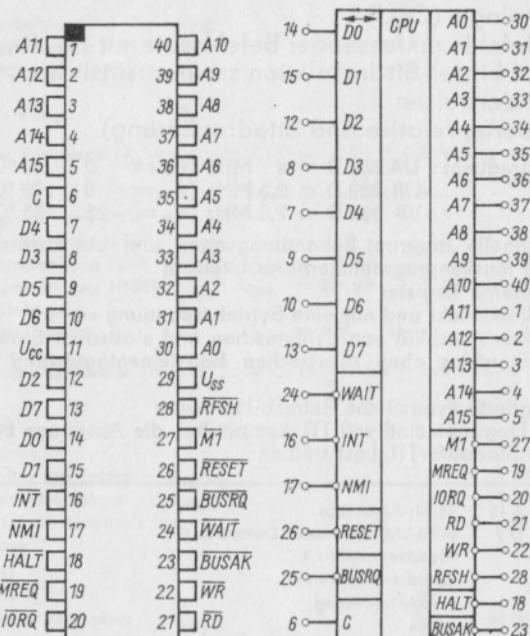

|                |                                |

|----------------|--------------------------------|

| A 0 . . . A 15 | 16-Bit-Adressbus               |

| D 0 . . . D 7  | 8-Bit-bidirektionaler Datenbus |

| M 1            | Maschinenzyklus 1              |

| <u>MREQ</u>    | Speicheranforderung            |

| <u>IORQ</u>    | E/A-Anforderung                |

| <u>RD</u>      | Lesen                          |

| <u>WR</u>      | Schreiben                      |

| <u>RFSH</u>    | Auffrischen der Information    |

| <u>HALT</u>    | Halt-Zustand                   |

| <u>WAIT</u>    | Warte-Signal                   |

| <u>INT</u>     | Maskierter Interrupt-Eingang   |

| <u>NMI</u>     | nichtmaskierter Interrupt      |

| <u>RESET</u>   | Rückstelleingang               |

| <u>BUSRQ</u>   | Bus-Anforderung                |

| <u>BUSA</u>    | Bus-Anforderungsbestätigung    |

## Bauform 17

## Anschlußbelegung und Schaltungskurzzeichen

### Grenzwerte: (Bezugspotential Uss = 0 V)

|                     |       | min  | max    |

|---------------------|-------|------|--------|

| Betriebsspannung    | Ucc   | -0,5 | 7 V    |

| Eingangsspannung    | Ui    | -0,5 | 7 V    |

| Lagerungstemperatur | θ_stg | -55  | 125 °C |

| Verlustleistung     | Pv    |      | 1,1 W  |

### Statische Kennwerte ( $\theta_a = 0 \dots 70^\circ\text{C}$ , $Ucc = 5 \text{ V} \pm 0,25 \text{ V}$ , $Uss = 0 \text{ V}$ )

|                           | Meßbedingungen | min                                 | max    |

|---------------------------|----------------|-------------------------------------|--------|

| Eingangsspannung LOW      | UIL            | -0,5                                | 0,8 V  |

| Eingangsspannung HIGH     | Uih            | 2,0                                 | Ucc V  |

| Ausgangsspannung LOW      | Uol            | Iol = 1,8 mA                        | 0,4 V  |

| Ausgangsspannung HIGH     | Uoh            | Ioh = -100 μA                       | 2,4 V  |

| Stromaufnahme             | Icc            | t <sub>c</sub> = 400 ns             | 200 mA |

| Eingangsreststrom         | Iu             | U <sub>i</sub> = 0 V ... Ucc        | 10 μA  |

| Taktkapazität             | Cc             | θ <sub>a</sub> = 25 °C              | 60 pF  |

| Eingangskapazität         | Ci             |                                     | 7 pF   |

| Takteingangsspannung LOW  | Uilc           | -0,5                                | 0,45 V |

| Takteingangsspannung HIGH | Uihc           | Ucc - 0,2                           | Ucc V  |

| Ausgangskapazität         | Co             | f = 1 MHz<br>θ <sub>a</sub> = 25 °C | 10 pF  |

### Dynamische Kennwerte ( $\theta_a = 0 \dots 70^\circ\text{C}$ , $Ucc = 5 \text{ V} \pm 0,25 \text{ V}$ , $Uss = 0 \text{ V}$ )

|                                     | min                             | max          |

|-------------------------------------|---------------------------------|--------------|

| UA 880 D                            |                                 |              |

| Taktperiode                         | t <sub>c</sub>                  | 250 1) ns    |

| High-Breite des Taktes              | tw(CH)                          | 105 2 000 ns |

| Low-Breite des Taktes               | tw(CL)                          | 105 2 000 ns |

| Anstiegs- und Abfallzeit des Taktes | t <sub>r</sub> , t <sub>f</sub> | 30 ns        |

### UB 880 D, VB 880 D

|                                     | min                             | max          |

|-------------------------------------|---------------------------------|--------------|

| Taktperiode                         | t <sub>c</sub>                  | 400 1) ns    |

| High-Breite des Taktes              | tw(CH)                          | 180 2 000 ns |

| Low-Breite des Taktes               | tw(CL)                          | 180 2 000 ns |

| Anstiegs- und Abfallzeit des Taktes | t <sub>r</sub> , t <sub>f</sub> | 30 ns        |

1)

$$1) \quad t_c = tw(CH) + tw(CL) + t_r + t_f$$