U(CS0) 0.14

U(CS1) 0.15

U(CS2) 0.16

U(CS3) 0.17

U(RCSM) 0.18

|                      |  |  |

|----------------------|--|--|

| 251-05-2731-2104 B12 |  |  |

| REF K2572            |  |  |

| Gesamtansicht        |  |  |

| VZG                  |  |  |

| Typ                  |  |  |

| Stckzahrschein       |  |  |

| Typ 012 - T102       |  |  |

| Stromaufteilung      |  |  |

| VEB Robotron         |  |  |

| ZFT                  |  |  |

| 1.12.81 7102 0/04    |  |  |

Betriebsdokumentation

K 1520

Heft 1

## Korrekturblatt

Ausgabe: 1/84

In der Ihnen übergebenen Betriebsdokumentation K 1520, Heft 1 werden folgende Korrekturen wirksam:

Seite Korrekturen

---

VII - 15 Pkt. 3.4.2.3 folgender Text kommt hinzu:

X 10 : 4 - X 11 : 4 : Masse C L K / T R G Ø

- Verwendung zur Mehrrechner-Kopplung

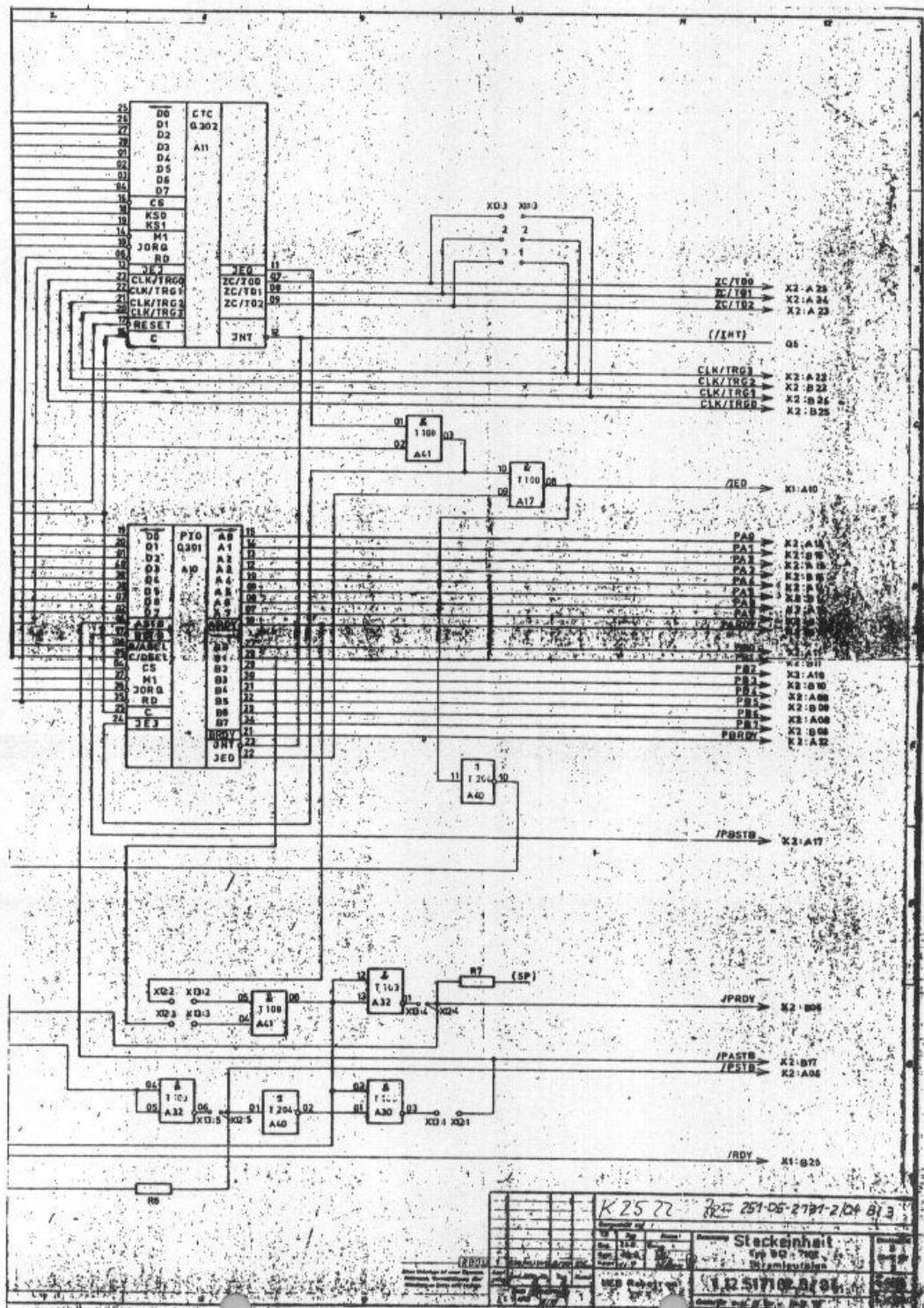

Die Mehrrechnerkopplung verwendet einen Koppelbus aus 8 Datenleitungen, 2 Datensynchronisationsleitungen, 7 Leitungen zur Adressierung, Quittierung und Statuskennzeichnung, eine Leitung zur Verbindung der /RESET-Signale und (bei Verwendung eines zentralen Taktgenerators) eine Leitung zur Verteilung des zentralen Taktes. Sie sind logisch und elektrisch aufeinander abgestimmt und werden über alle vier Rechner durchgehend verdrahtet. Konstruktiv sind die Signale wie folgt angeordnet:

| Signalname | Klemme der Steckleinheit |

|------------|--------------------------|

| PA0        | X2:A16                   |

| PA1        | X2:B16                   |

| PA2        | X2:A15                   |

| PA3        | X2:B15                   |

| PA4        | X2:A14                   |

| PA5        | X2:B14                   |

| PA6        | X2:A13                   |

| PA7        | X2:B13                   |

| /PRDY      | X2:B06                   |

| /PSTB      | X2:A06                   |

| PB0        | X2:A11                   |

| PR2        | X2:A10                   |

| PR3        | X2:B10                   |

| PR4        | X2:A09                   |

| PR5        | X2:B09                   |

| PR6        | X2:A08                   |

| PR7        | X2:B08                   |

| /RESET     | X2:B05                   |

| TAKTO      | X2:B04                   |

- Datenleitungen

- Datensynchronisationsleitungen

- Statuskennzeichnung

- Leitungen zur Adressierung und Quittierung

Rücksetzen des Mehrrechnersystems

Zentraler Takt des Mehrrechnersystems (falls verwendet)

VII-20

1.12.517101.0/61

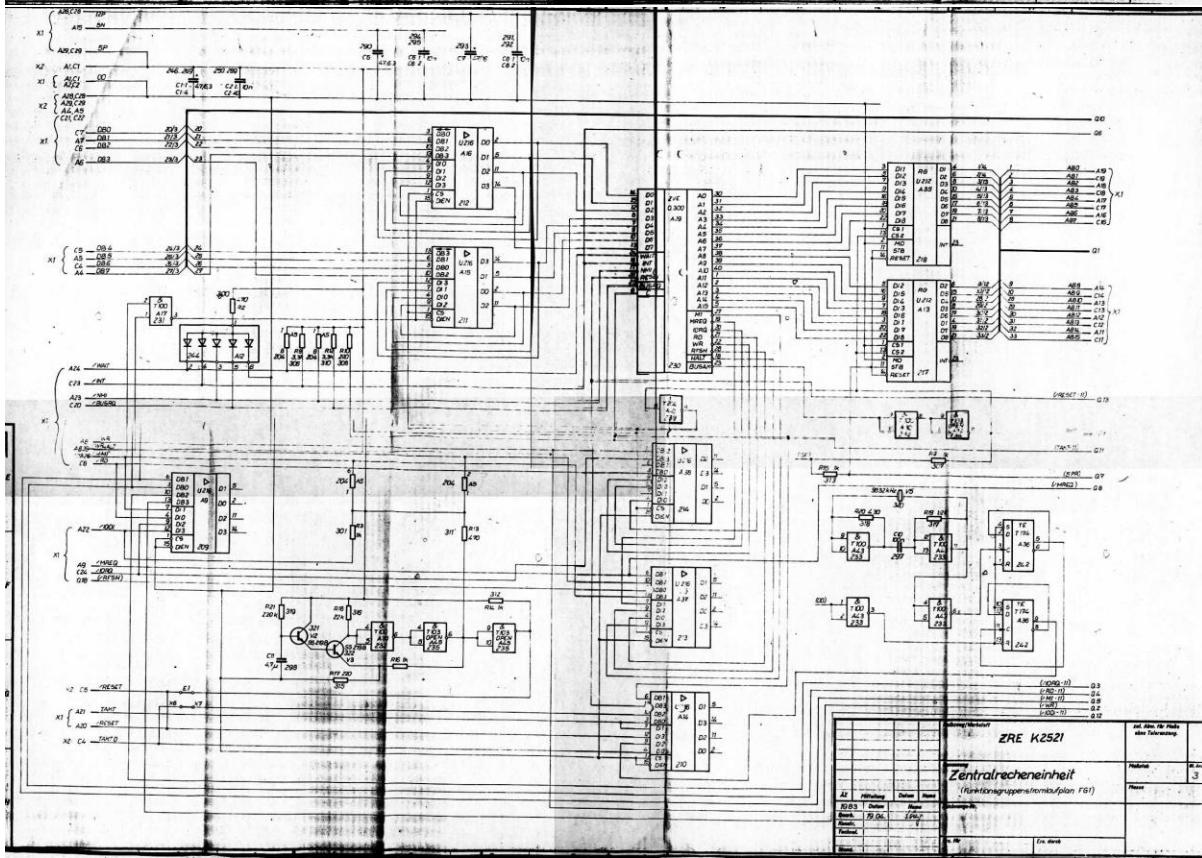

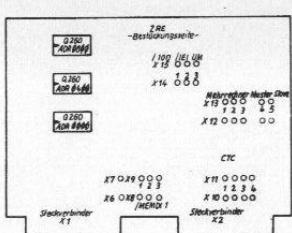

### 3.5. Parallele Ein/Ausgabe

#### 3.5.1. Struktur

Die Schaltung zur parallelen Ein- und Ausgabe besteht aus dem Schaltkreis Q301, einer Ergänzungselektronik und einer Koppel- elektronik. Die Ergänzungselektronik dient der Anpassung des Q301 an die elektrischen und logischen Bedingungen des System- busse K 1520. Sie wird bei den Typen K 2521 und K 2522 mit dem Q302 gemeinsam genutzt und besteht aus Datenverstärkern mit Richtungssteuerlogik, Adressenentschlüsselung zur Bildung der CS-Signale und des RDY-Signals, der Auswahl des DEI- Signals mit einer Look-Ahead-Carry-Schaltung sowie einigen Verstärkern. Der Q301 kann zur Kopplung von bis zu vier K 1520 benutzt werden. Er besitzt dazu eine Koppel elektronik zur Synchronisierung des Datensustausches. Diese kann durch Wickelverbindungen von Q301 getrennt oder für die Verwendung als Master- bzw. Slave-Rechner verdreht werden (siehe Abb. VII/2 und Tabelle 1).

Tabelle 1:

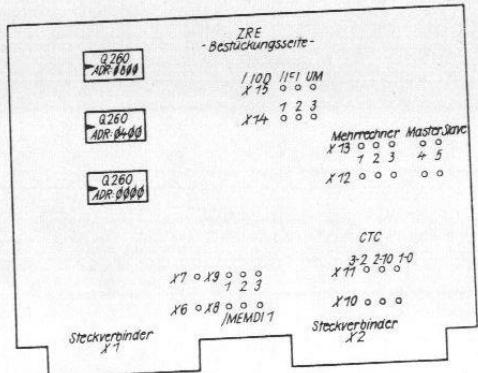

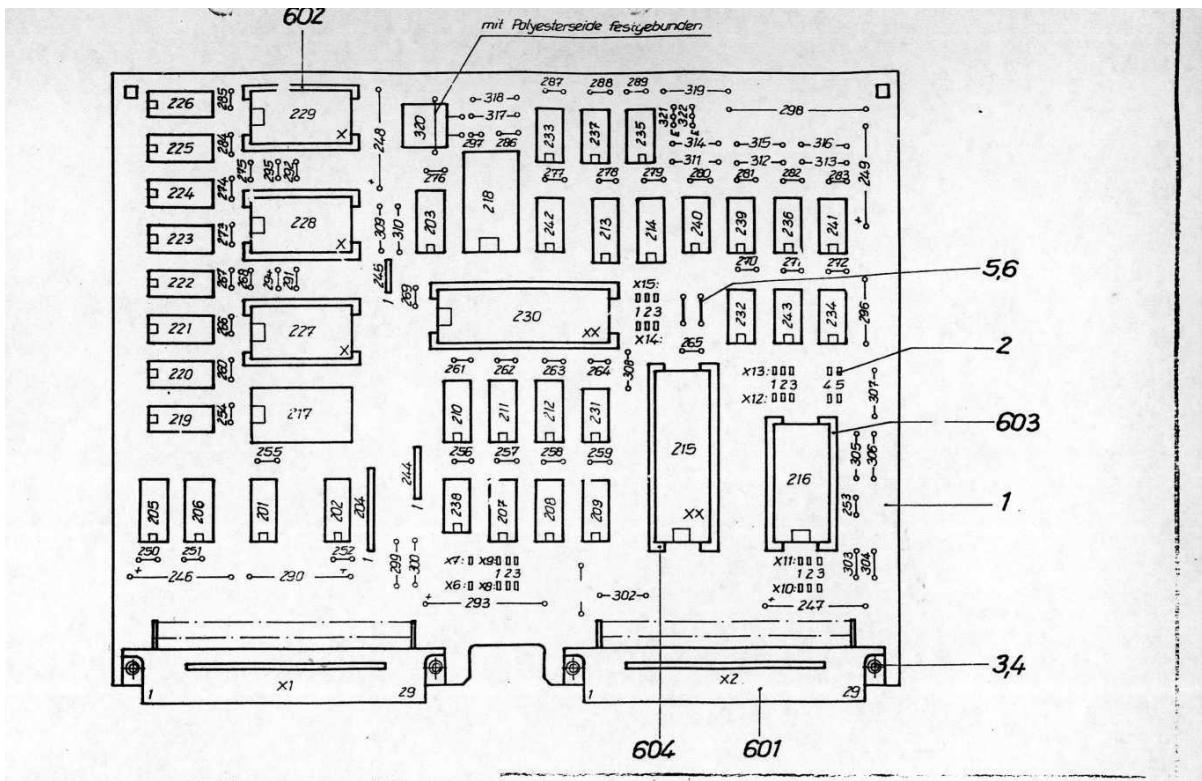

Festlegung des Regimes der ZRE durch die Wickelbrücken X12/X13

| Regime                | X12:1 | :2 | :3 | :4 | :5 |

|-----------------------|-------|----|----|----|----|

|                       | X13:1 | :2 | :3 | :4 | :5 |

| <b>Einzelrechner</b>  |       |    |    |    |    |

| Mehrrechner<br>Master | x     | x  | x  | x  |    |

| Mehrrechner<br>Slave  | x     | x  | x  | x  |    |

x = Wickelbrücke vorhanden

#### 3.5.2. Anschlußbedingungen

##### 3.5.2.1. Systembus

Die elektrischen und logischen Bedingungen der Ein-/Ausgabe entsprechen denen des Systembusses K 1520, lt. TGL 37271.

##### 3.5.2.2. Koppelbus

- Verwendung zur parallelen Ein- und Ausgabe

Die elektrischen und logischen Bedingungen entsprechen denen des Schaltkreises Q301. Konstruktiv sind Signale wie folgt angeordnet:

| Q301-Bezeichnung | Signalname | Klemme der Steckleinheit |

|------------------|------------|--------------------------|

| A0               | PA0        | X2:A16                   |

| A1               | PA1        | X2:B16                   |

| A2               | PA2        | X2:A15                   |

| A3               | PA3        | X2:B15                   |

| A4               | PA4        | X2:A14                   |

| A5               | PA5        | X2:B14                   |

| A6               | PA6        | X2:A13                   |

| A7               | PA7        | X2:B13                   |

| ARDY             | PARDY      | X2:B12                   |

| /ASTB            | /PASTB     | X2:B17                   |

| B0               | PB0        | X2:A11                   |

| B1               | PB1        | X2:B11                   |

| B2               | PB2        | X2:A10                   |

| B3               | PB3        | X2:B10                   |

| B4               | PB4        | X2:A09                   |

| B5               | PB5        | X2:B09                   |

| B6               | PB6        | X2:A08                   |

| B7               | PB7        | X2:B08                   |

| BRDY             | PBRDY      | X2:A12                   |

| /BSTB            | /PBSTB     | X2:A17                   |

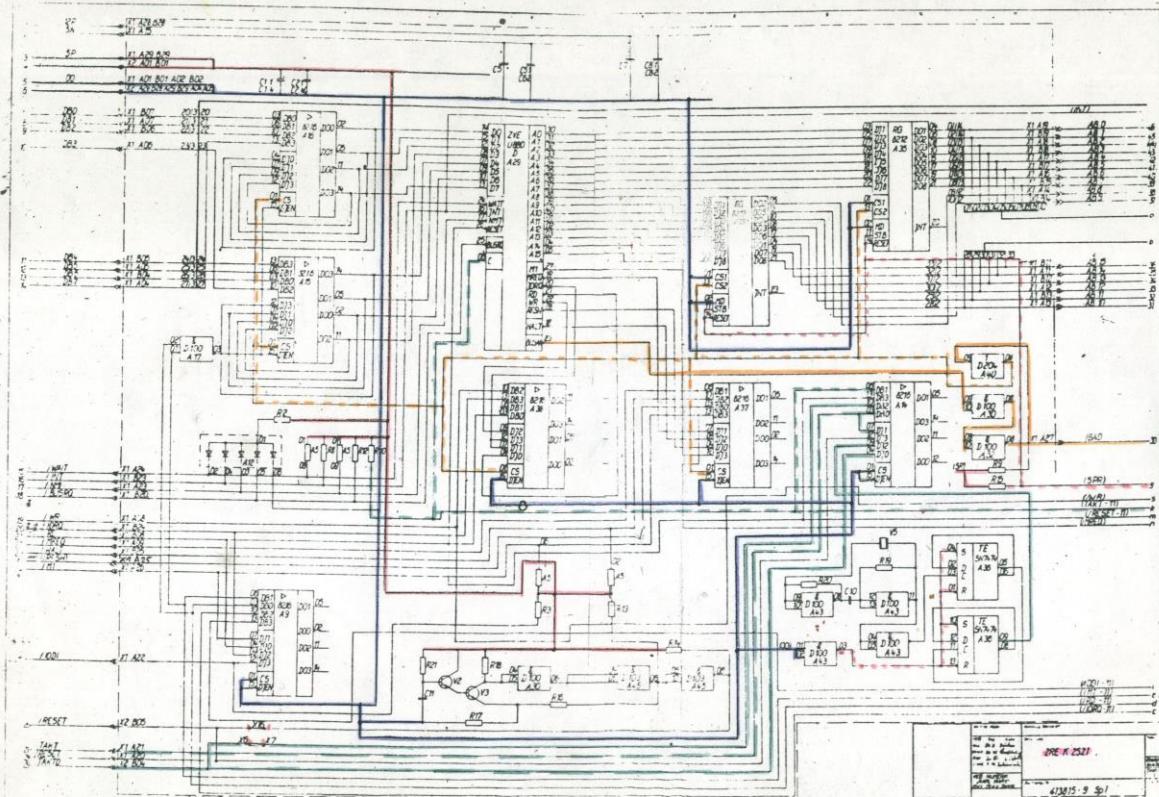

#### 3.4.2.3. Funktion

Der Anwender kann alle Möglichkeiten nutzen die der Schaltkreis Q302 bietet. Die oben angeführten Signale werden unbeschaltet zur Verfügung gestellt.

Durch Wickelbrücken können die Kanäle aber auch wie folgt im Reihe geschaltet werden:

|                 |        |          |

|-----------------|--------|----------|

| X10:3 - X11:3 : | ZC/T06 | CLK/TRG1 |

| X10:2 - X11:2 : | ZC/T01 | CLK/TRG2 |

| X10:1 - X11:1 : | ZC/T02 | CLK/TRG3 |

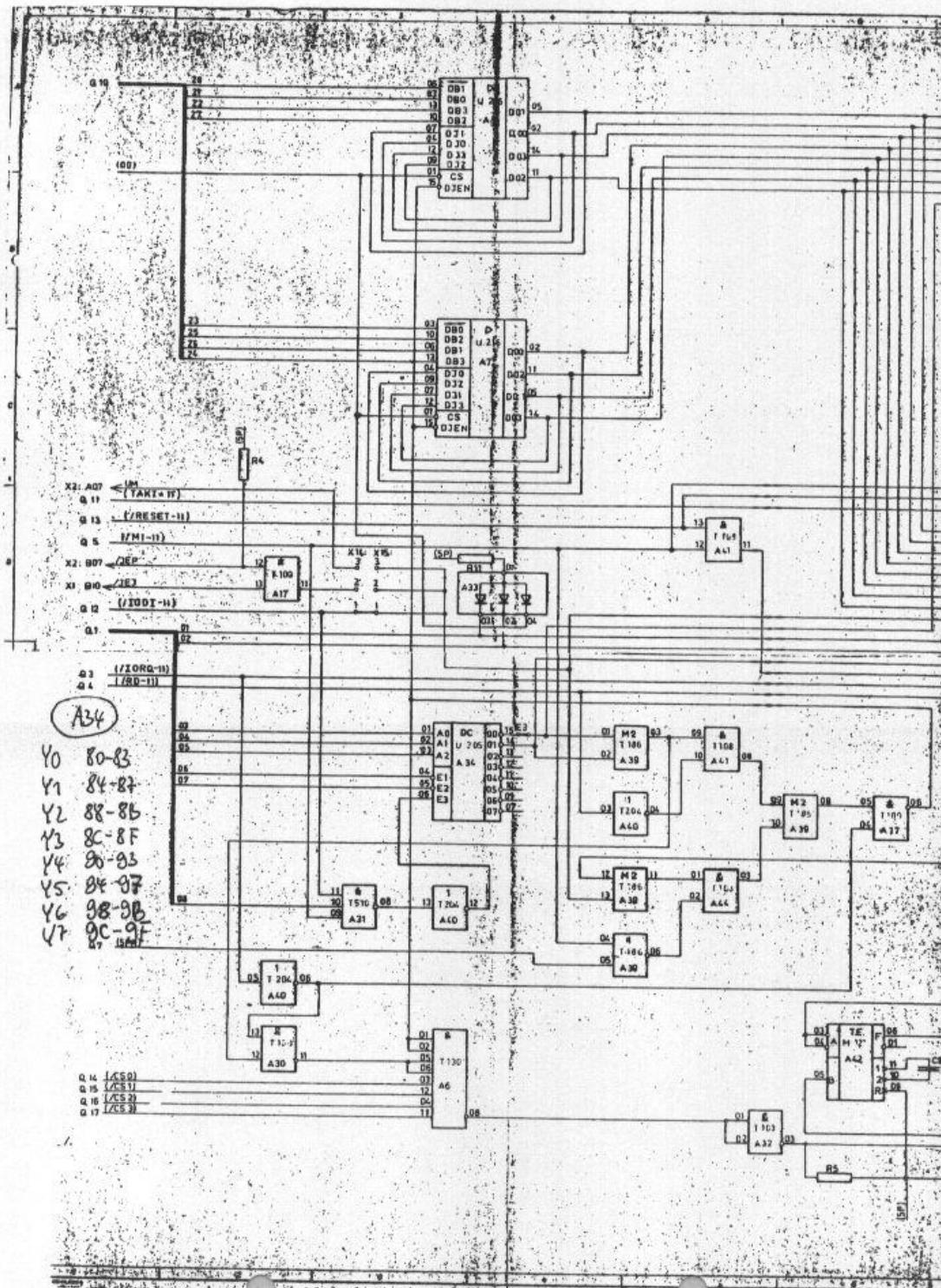

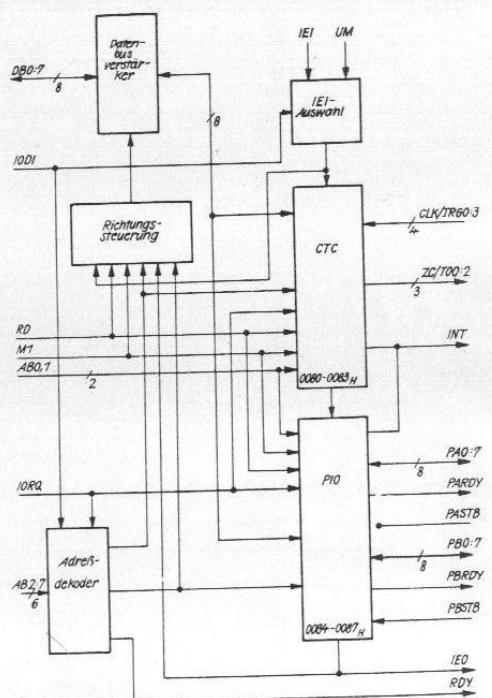

Der Schaltkreis wird vom Systembus über die Ergänzungselektronik angesteuert, falls auf dem Adressbus AB7 bis ABO die Adressen  $80_H$  bis  $83_H$  liegen, /IODI, /M1 high und /IORQ low sind. Die Verdrahtung der Bits AB0 und AB1 realisiert folgende Bedeutung der Adressen:

| AB7:0  | Kanal |

|--------|-------|

| $80_H$ | 0     |

| $81_H$ | 1     |

| $82_H$ | 2     |

| $83_H$ | 3     |

Der Q302 besitzt in der Interruptkette der ZRE die höchste Priorität. Der Datenbuspuffer ist bidirektional und wird in Richtung Systembus gesteuert, wenn der Q302 ausgewählt wird und dabei /RD = low ist (Lese-Zugriff) oder /IORQ und /M1 low, /IEI und /IEB high sind (Unterbrechungsquittierung). Bei Ein- und Ausgabezugriff sowie Interruptanerkennung wird jeweils /RDY auf low gezogen.

VII-16 1.12.517101.0/61

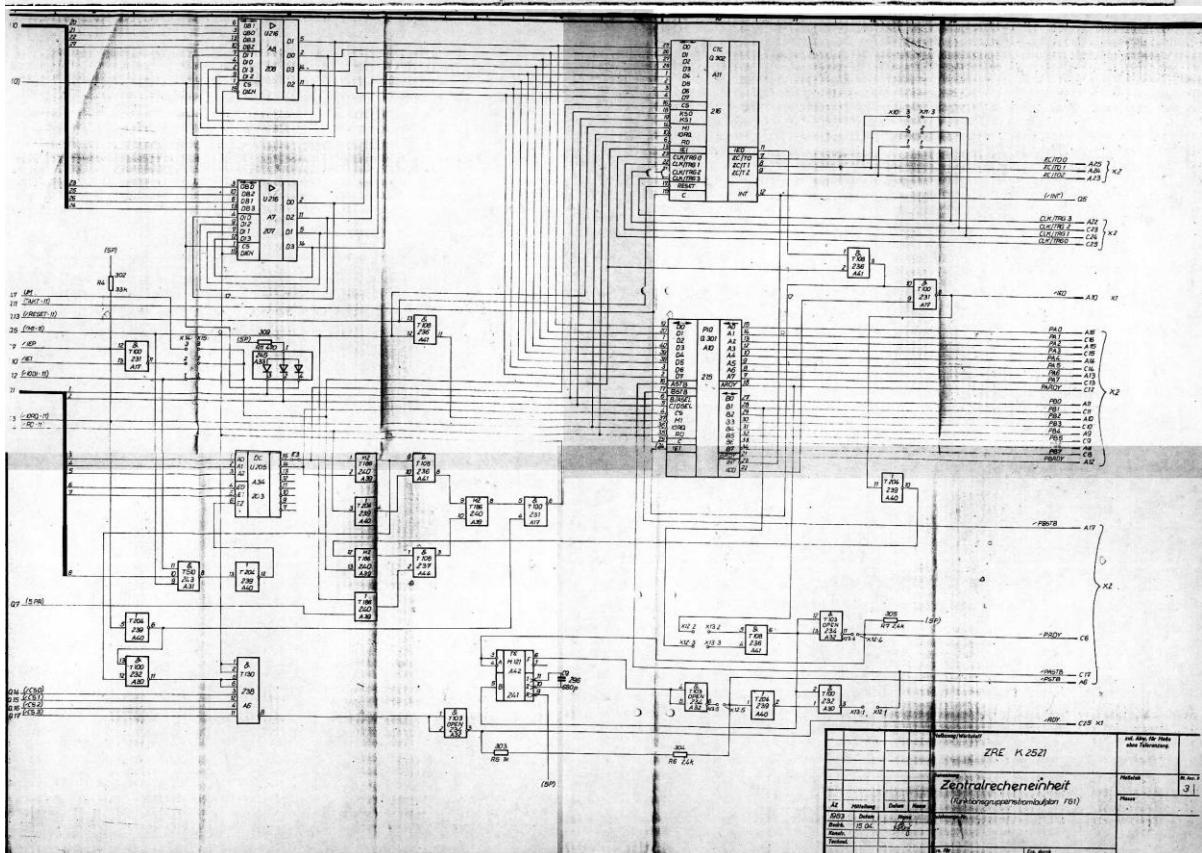

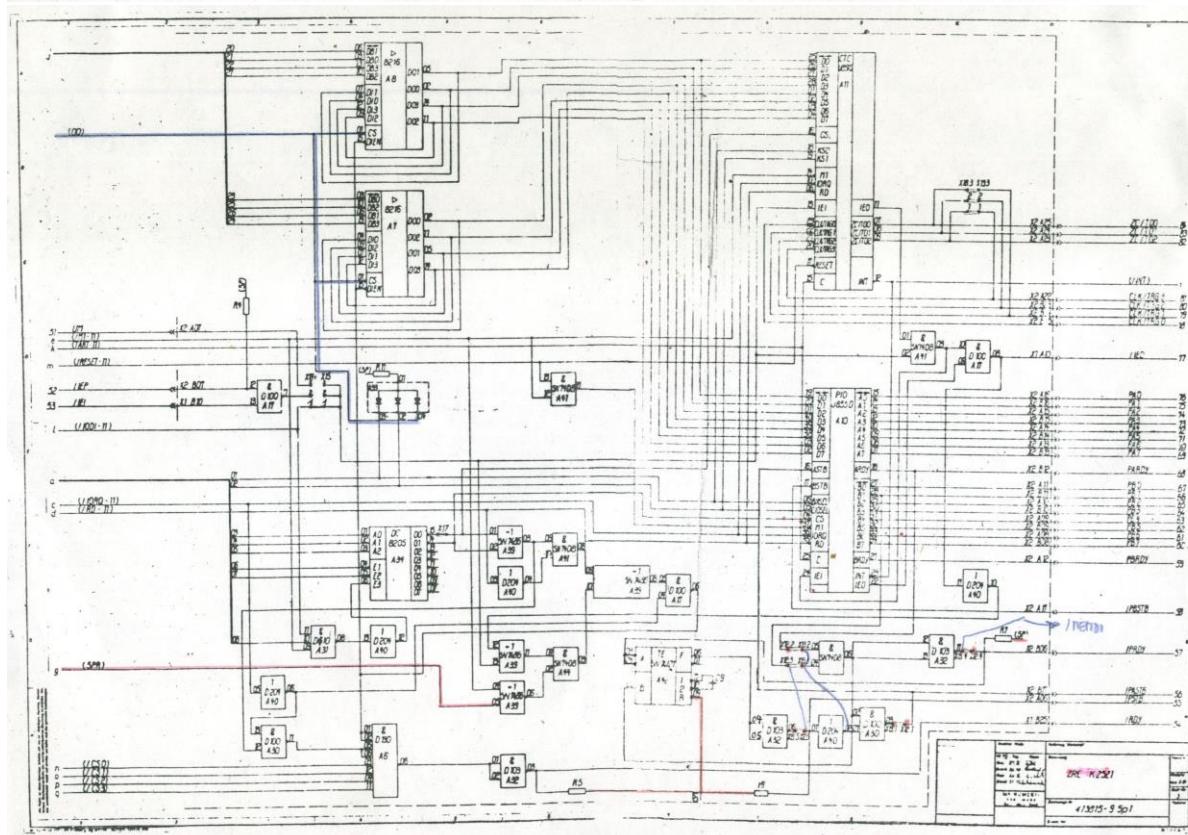

Abb. VII/4 Logische Struktur von Zähler/Zeitgeber und Parallel-SIM- und Ausgabeinterface (ohne Koppel- elektronik)

VII-17 1.12.517101.0/61

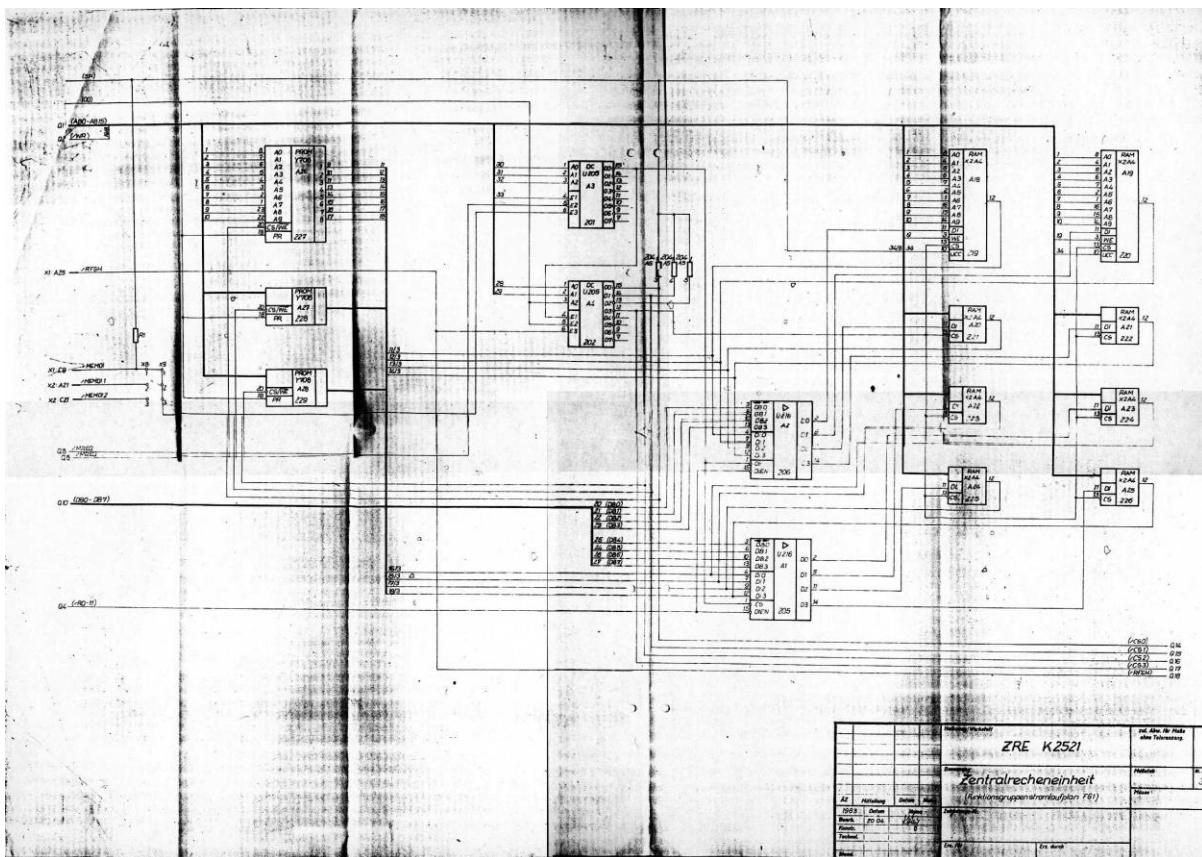

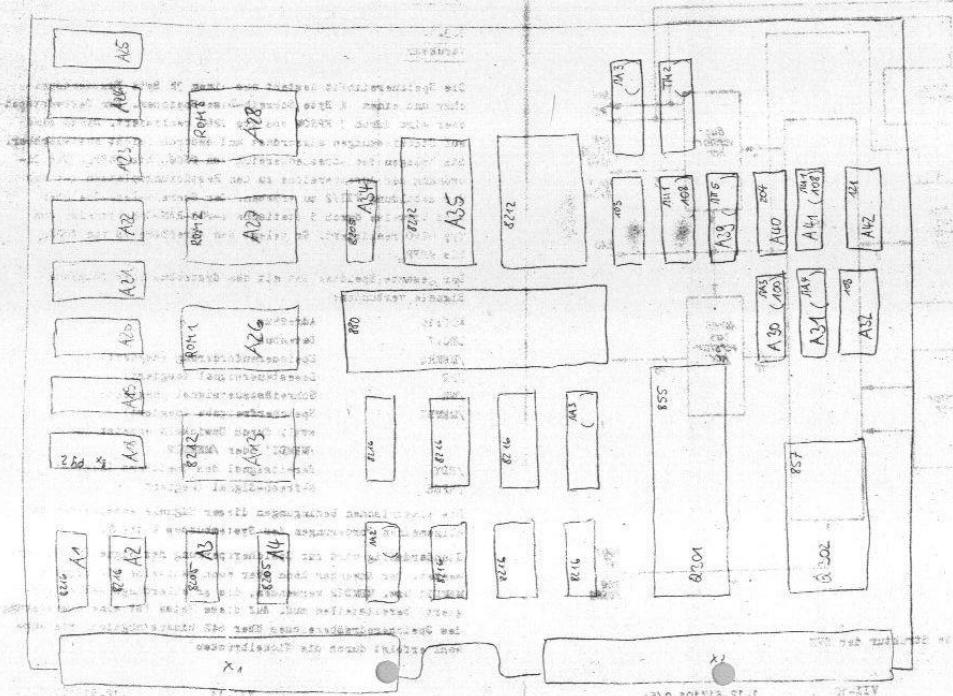

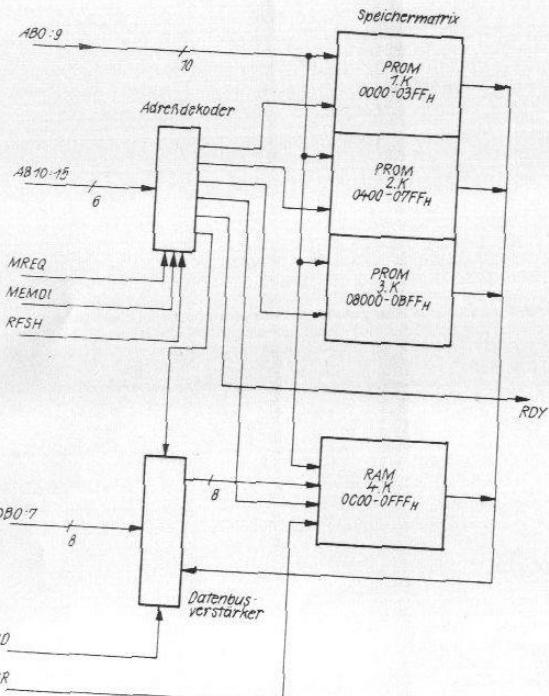

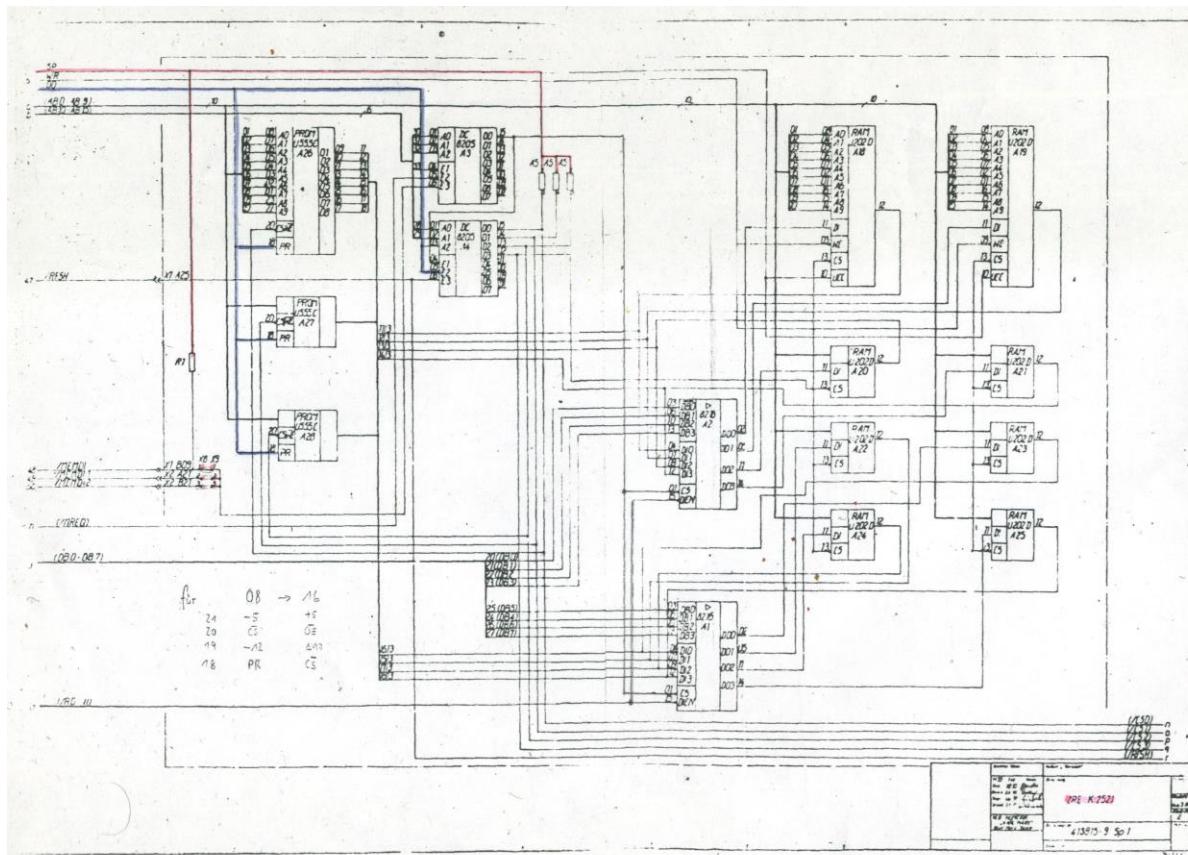

Abb. VII/3 Logische Struktur des Speichers der ZRE

VII-14 1.12.517101.0/61

#### 3.4.1. Struktur

Der Zähler/Zeitgeber besteht aus dem Schaltkreis Q302 und der Ergänzungselektronik. Die Ergänzungselektronik dient der Anpassung des Q302 an die elektrischen und logischen Bedingungen des Systembusses K 1520. Sie wird mit dem Q301 gemeinsam benutzt und besteht im wesentlichen aus Datenpuffer mit Richtungssteuerung und Adressenentschlüsselung zur Bildung des Bausteineinwähl- und RDY-Signals.

#### 3.4.2. Anschlußbedingungen

##### 3.4.2.1. Systembus

Die elektrischen und logischen Bedingungen des CTC entsprechen denen des Systembusses K 1520, lt. TGL 37271.

##### 3.4.2.2. Koppelbus

Die anwenderspezifischen Sim- und Ausgangssignale des Q302 sind an dem Koppelbus geführt und konstruktiv wie folgt angeordnet:

| Steckver.-Klemme                 |        |

|----------------------------------|--------|

| CLK/TRG0                         | I2:B25 |

| CLK/TRG1                         | I2:B24 |

| CLK/TRG2                         | I2:B23 |

| CLK/TRG3                         | I2:A22 |

| Nulldurchgangs-/Triggersausgänge |        |

| ZG/T00                           | I2:A25 |

| ZG/T01                           | I2:A24 |

| ZG/T02                           | I2:A23 |

VII-15 1.12.517101.0/61

X8:1 - X9:1 für /MEMDI

X8:2 - X9:2 für /MEMDI1

X8:3 - X9:3 für /MEMDI2

Deren Lage ist in Abb. VII/2 erkennbar.

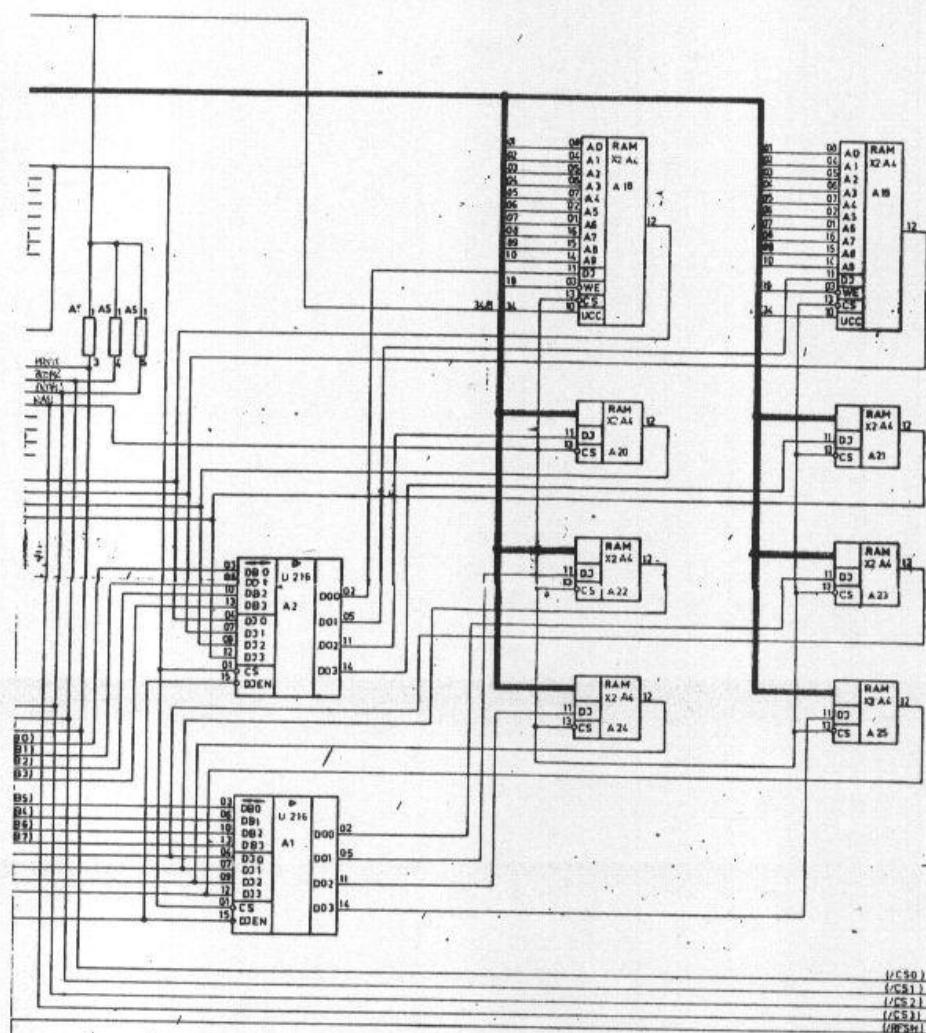

Abb. VII/3 zeigt die Blockstruktur der Speicherseinheit.

### 3.3.2. Funktion

Die Aktivierung des Speichers erfolgt durch /MREQ = low, falls AB12 bis AB15 low /RFSH, /MEMDI bzw. /MEMDI1 bzw. /MEMDI2 (je nach Verdrachtung) high sind. Daraufhin wird das Signal /RDY (offener Kollektor) auf low gezogen, die Decodierung der Adressbits AB10 und AB11 sowie der Datenbusverstärker aktivierte. Dabei werden vier CS-Signale gebildet, die zur Ansteuerung der vier 16 Byte-Speichermatrixen dienen. Auf welchen Byte innerhalb der Matrix zugegriffen wird, entscheiden die die Speicherhalskriese direkt steuern Adressbits AB0 bis AB9. Beim RAM bewirkt das Signal /WR = low das Einschreiben der verstärkten Datenbussignale DBO bis DB7 in den Speicher. Dabei ist der DB-Puffer durch /RD = high in Richtung zum Speicher gesteuert und legt die Daten an dessen Eingänge. Beim Lesen wird der DB-Puffer durch /RD = low in Richtung Systembus gesteuert und das von der mit CS aktivierte Speichermatrix gelieferte Datenbyte verarbeitet.

### 3.4. Zähler/Zeitgeber

Der Zähler/Zeitgeber ist nur auf den Typen K 2521 und K 2522 realisiert.

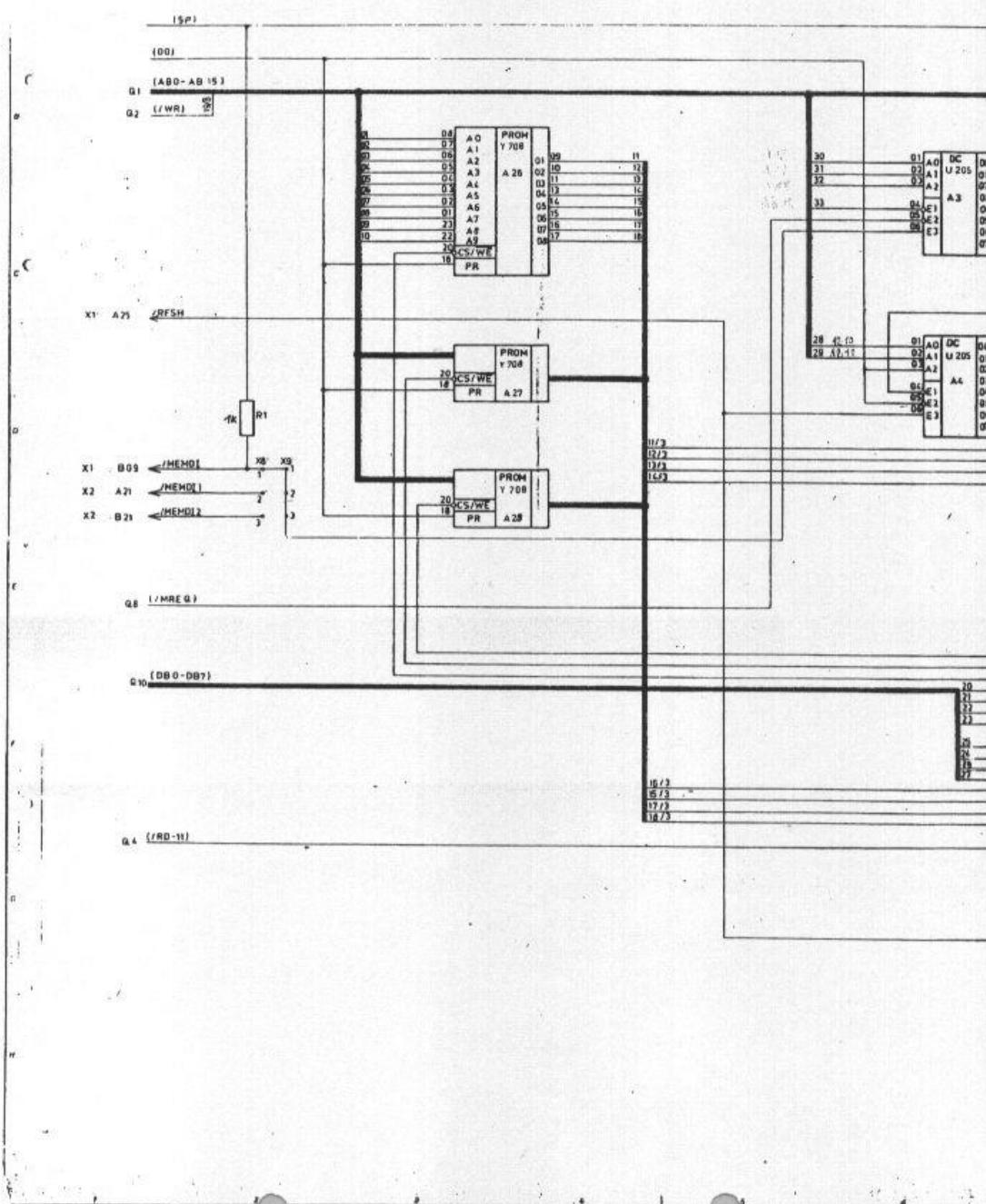

Abb. VII/2 Zentrale Bedieneinheit K 2521 ... K 2524

Adressenzuordnung der PROM-Plätze und

Anordnung der Wickelbrücken

VII-13 1.12.517101.0/61

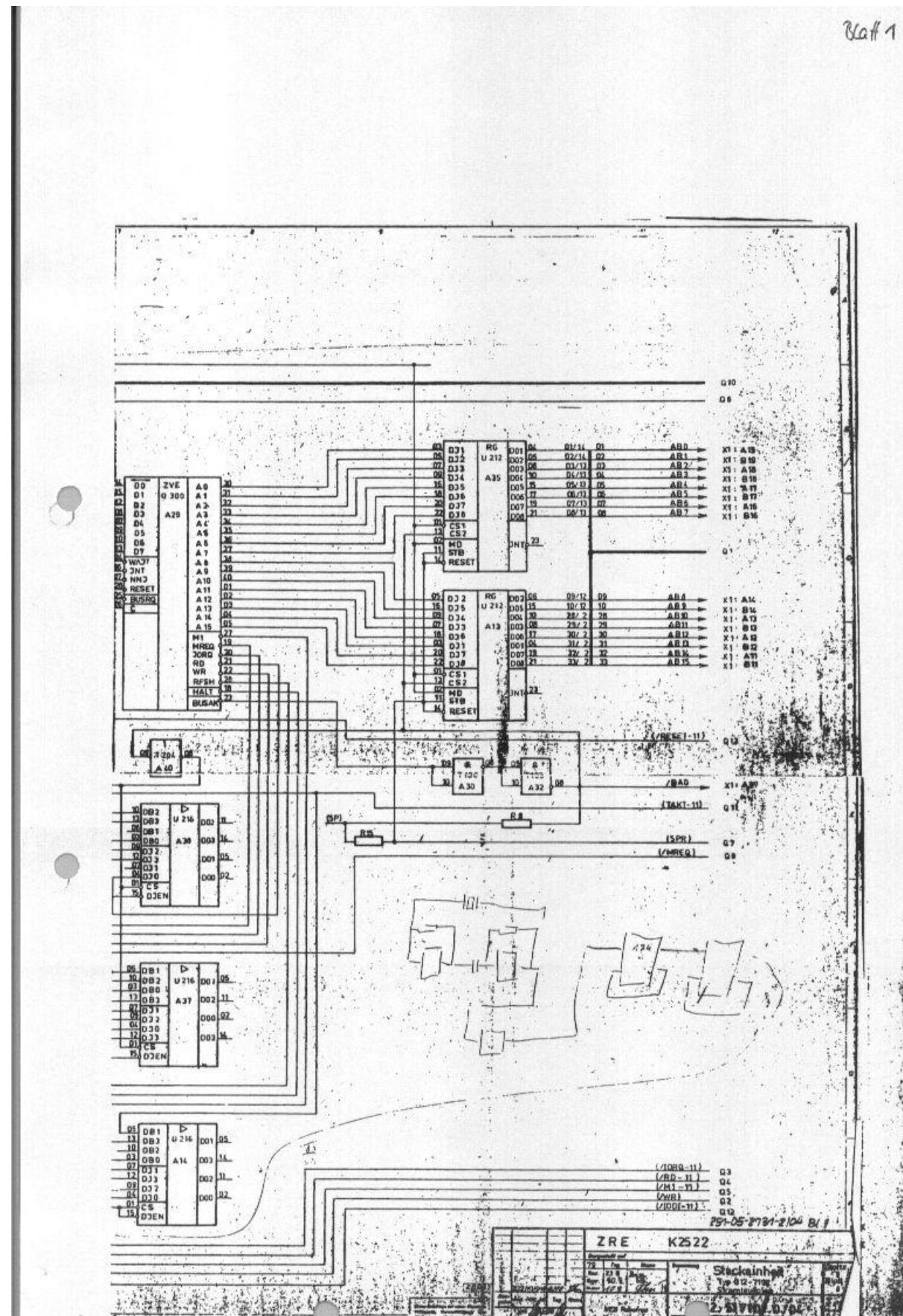

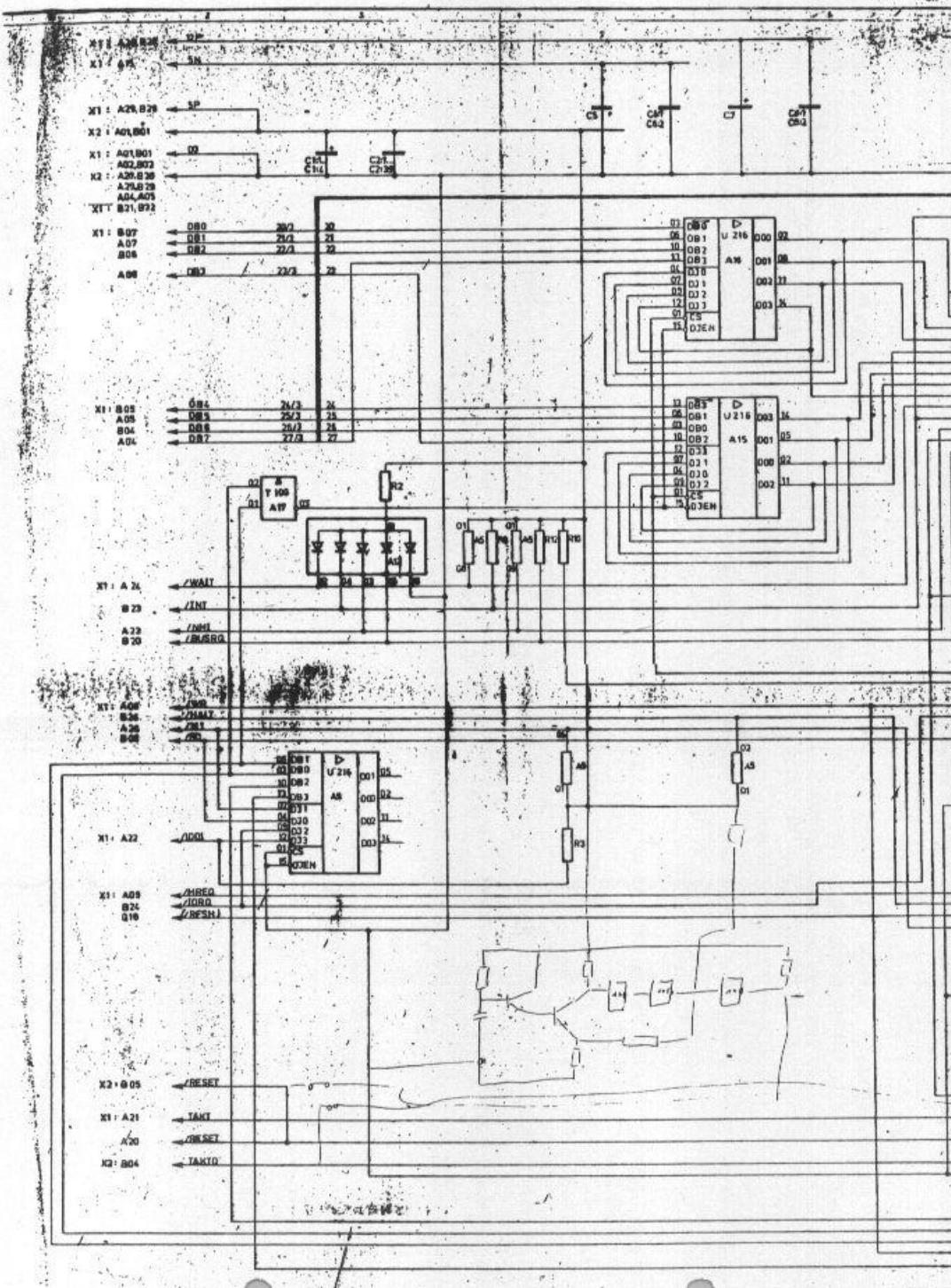

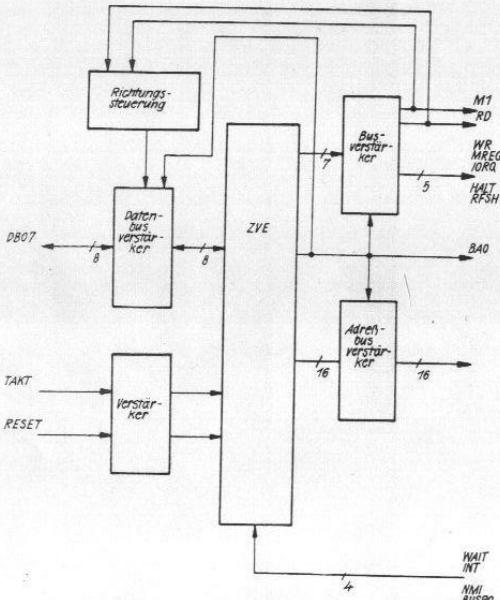

Abb. VII/1 Logische Struktur der ZVE

### 3.3. Speicher

### 3.3.1.

Die Speichereinheit besteht aus einem 3K Byte Festwertspeicher und einem 1K Byte Schreib-Lesen-Speicher. Der Festwertspeicher wird durch 3 EPROM vom Typ O260 realisiert. Diese sind auf Steckfassungen angeordnet und dadurch leicht austauschbar. Sie belegen den Adressenbereich von  $0000_8$  bis  $0FFF_8$ . Die Zuordnung der Adressbereiche zu den Beleuchtungspunkten ist aus der Abbildung VII/2 zu ersehen. Der Schreib-Lesen-Speicher wird bitweise durch 8 statische n-MOS-RAM-Schaltkreise vom Typ O240 realisiert. Er belegt den Adressbereich von  $9000_8$  bis  $FFFF_8$ .

Der gesamte Speicher ist mit dem Systembus über folgende Signale verbunden:

|         |                                      |

|---------|--------------------------------------|

| AB0:15  | Adressebus                           |

| DB0:7   | Datenbus                             |

| /MEMREQ | Speicheranforderung (negiert)        |

| /RD     | Lesesteuersignal (negiert)           |

| /WR     | Schreibsteuersignal (negiert)        |

| /MEMDI  | Speicherfreigabe (negiert)           |

|         | evtl. durch Umwickeln ersetzt durch  |

|         | /MEMDI1 oder /MEMDI2                 |

| /RDY    | Bereitschaft des Speichers (negiert) |

| /RPSH   | Refresh-Signal (negiert)             |

Die elektrischen Bedingungen dieser Signale entsprechen den allgemeinen Forderungen des Systembusses K 1520. Standardmäßig wird zur Speicherersperrung das Signal MEMDI verwendet. Der Anwender kann aber auch wahlweise die Signale MEMDI bzw. MEMDIZ verwenden, die er allerdings selbst (negiert) bereitstellen muß. Auf diese Weise ist eine Erweiterung des Speicheradreßbereiches über 64K hinaus möglich. Die Auswahl erfolgt durch die Wickelbrücken

Die Typen K 2521 und K 2523 erzeugen TAKTO selbst. Für die Typen K 2522 und K 2524 muß TAKTO von einem anderen Rechner (Mehrrechnersystem), vom Busverstärker K 4120 (Kopplung mit Entwicklungssystem) oder separat bereitgestellt werden.

#### 3.1.3. Rücksetzungsschaltung

Nach dem Einschalten der Betriebsspannung 5V wird ein Kondensator aufgeladen und mit einem Schwellwertschalter überwacht. Solange die Einschaltenschwelle noch nicht erreicht ist, wird das Systembussignal /RESET auf "low" über einen Treiber mit offenem Kollektor gezogen. Am Treiber ist ein Kollektowiderstand von 1K Ohm angeordnet. Damit werden folgende elektrische Daten realisiert:

$$\begin{aligned} U_{OL} &= 0,4 \text{ V für } I_{OL} = 5 \text{ mA} \\ U_{OH} &= 2,4 \text{ V für } I_{OH} = 2,25 \text{ mA.} \end{aligned}$$

Die Zeit vom Zuschalten der 5V bis zur "low-high"-Flanke von /RESET beträgt mindestens 300 ms.

#### 3.2. Zentrale Verarbeitungseinheit (ZVE)

##### 3.2.1. Struktur

Die ZVE besteht aus dem Mikroprozessor (MP) Q300 und der Ergänzungselektronik. Der MP realisiert die logischen Funktionen der ZVE. Die Ergänzungselektronik ergänzt und setzt die elektrischen Bedingungen für die Ankopplung an den Systembus des MR K 4120 und besteht aus folgenden Komponenten:

- Verstärker für /RESET und TAKT (mit Ziemwiderstand zur Pegelaushebung; mitbenutzt von PIO und CPU).

- Arbeitswiderstände und Abblockdioden für ZVE-Steuereignisse mit offenem Kollektor bzw. Dsein (/NMI, /WAIT, /INT, /BUSRQ).

- Bildung der Bus-Anforderungsbestätigung /BAO durch eine Stufe mit offenem Kollektor (zum Zweck des externen BUS-Abschaltens im WAIT-Zustand) aus dem Signal /BUSAK.

- Verstärker für Adressbus ABO:15, Datenbus DBO:7 und Systemsteuersignale /MREQ, /M1, /IORQ, /RD, /WR, /RFSH, /HALT, die mit BAO hochohmig geschaltet werden: /M1 und /HALT besitzen Ziemwiderstände, die dann an ihnen High-Pegel erzeugen. Nur die Datenbusverstärker erbeiten bidirektional und werden mit RD oder M1 in Richtung ZVE gesteuert.

#### 3.2.2. Funktion

Die Aufgabe der ZVE besteht in der Abarbeitung der im Speicher stehenden Programme und in der Reaktion auf Unterbrechungssignale von externen Einheiten.

Dazu muß die ZVE über den Systembus mit den Speichern und E/A-Einheiten Informationen austauschen.

Die Ergänzungselektronik hat keinen Einfluß auf die Funktion des Schaltkreises Q300. All seine programmtechnischen Eigenschaften sind nutzbar.

Folgende elektrische Besonderheiten sind allerdings zu beachten:

- Im Ruh Zustand verstarken die Datenbustreiber in Richtung Systembus

- Auf der ZVE sind alle Widerstände der Systembusleitungen für offenen Kollektor bzw. Dsein vorhanden

- /BAO ist mit offenem Kollektor ausgeführt

- Auch /RFSH, /M1 und /HALT werden bei BUSAK hochohmig geschaltet. /M1 und /HALT werden aber dabei durch Widerstände auf high gezogen.

#### Zeitgeber:

Erzeugbare Intervalle: programmierbar ( $16 \dots 256^2$ )  $\cdot t_z$

$t_z$  = Systemtakzyklus

#### Zähler

Zählerbereich: programmierbar

$1 \dots 256$  externe Ereignisse

Max. Zahlbereich: 256<sup>2</sup> externe Ereignisse;

erreichbar durch Reihenschaltung von 4 Kästchen

#### 2.6. Parallel-Zin/Ausgabe (PIO)

|                                       |                                         |

|---------------------------------------|-----------------------------------------|

| Schaltkreistyp:                       | Q301 (siehe 2.6.)                       |

| Anzahl der Ports:                     | 2 (Port A, Port B)                      |

| (bzw. bidirektionale Interfacekanäle) |                                         |

| Ausgangssignale:                      | MOS, TTL-kompatibel (max. 1,8 mA)       |

| Eingangssignale:                      | MOS, TTL-kompatibel                     |

| Adresseierung:                        | fest                                    |

| Adressen:                             | 0084 <sub>H</sub> ... 0087 <sub>H</sub> |

| Betriebsarten:                        | 4                                       |

#### 2.7. Mehrrechnerkopplung

|                                 |                                                                                                                         |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Schaltkreistyp:                 | Q301 (siehe 2.6.)                                                                                                       |

| Anzahl der koppelbaren Rechner: | max. 1 Master - mit 3 Slaverechnern                                                                                     |

| Übertragungsmodus:              | Interruptverkehr zwischen Prozessor und E/A-Ports, programmierten Datenblocktransfer zwischen Master- und Slaverechnern |

| Übertragungsgeschwindigkeit:    | 30k Byte/s                                                                                                              |

#### 3. Technische Beschreibung

##### 3.1. Takterzeugung und Rücksetzungsschaltung

Die unter Pkt. 3.1.1. und 3.1.3. beschriebenen Funktionseinheiten sind nur auf den Typen K 2521 und K 2523 vorhanden.

##### 3.1.1. Takterzeugung

Ein Quarzgenerator erzeugt eine Grundfrequenz von 9830,4 kHz  $\pm$  0,1 %. Diese wird mit Hilfe eines Dualzählers auf die Systemfrequenz von 2,4576 MHz  $\pm$  0,1 % geteilt (Testverhältnis 1:1). Ein folgender Treiber speist den Koppelbus mit dem Signal TAKTO. Diese Verbindung kann durch die Wickelbrücke X6 - X7 unterbrochen werden. Das ist z.B. notwendig, wenn der Takt unterbrochen wird, wenn dieser vom Entwicklungssystem über separaten erzeugt wird, wenn dieser vom Busverstärker K 4120 oder von einer anderen ZVE (s.a. Mehrrechnersystem) zugeführt wird. Der Treiber gewährleistet folgende elektrische Bedingungen:

$$\begin{aligned} \text{Low-Ausgangsspannung } U_{OL} &= 0,4 \text{ V bei } I_{OL} = 15 \text{ mA} \\ \text{High-Ausgangsspannung } U_{OH} &= 2,4 \text{ V bei } I_{OH} = 5 \text{ mA} \\ \text{Taktykluszeit } t_z &= 407 \text{ ns } \pm 0,1 \% \end{aligned}$$

##### 3.1.2. Taktentkopplung

Unabhängig vom Ort der Takterzeugung wird das Signal TAKTO auf dem Koppelbus eingespeist und kann hier an andere Rechner oder Geräte weitergeleitet werden. In jedem Falle wird auf der ZVE eine Taktentkopplung realisiert, indem das Signal TAKTO des Koppelbus verstärkt und als Signal TAKT an der entsprechenden Klemme des Systembus eingespeist wird.

# K 2521 - K2524

## 2. Technische Daten

### 2.1. Allgemeine Daten

Steckleinheitenabmessungen: 215 mm x 170 mm

Steckraster: 20 mm

Steckverbinder: 2 x 58polig, indirekt. Bauf. 304-58

TGL 29331/03 bzw.

2 x 58polig, direkt

TGL 29331/01

Einsatzklasse: 5/60/30/95/10-1g

Stromversorgung (typisch; alle PROMs bestückt):

K 2521 K 2522 K 2523 K 2524

5P = + 5 V  $\pm$  5 % 1,50 A 1,45 A 1,45 A 1,40 A

5N = - 5 V  $\pm$  5 % 0,07 A 0,07 A 0,07 A 0,07 A

12P = + 12 V  $\pm$  5 % 0,12 A 0,12 A 0,12 A 0,12 A

### 2.2. Taktzeugung

Quarztyp: Q51/E2010 TGL 33584

Quarzschwingschwingfrequenz: 9832 KHz

Systemtaktfrequenz: 2,4576 MHz  $\pm$  0,1 %

Systemtaktzyklus: 407 ns  $\pm$  0,1 %

### 2.3. Zentrale Verarbeitungseinheit

Schaltkreistyp: Q300 (ASSO)

Befehlsanzahl: 158 Basisbefehle

Befehslängen: 1, 2, 3 oder 4 Byte

Verarbeitungsbreite: 1 Byte

Wortlängen Daten: 1 oder 2 Byte

Adressierbarer Speicher: 64 K Byte

E/A-Adressbereich: 256 Ein-/256 Ausgabeadressen (erweiterbar)

Unterbrechungsarten:

1. maskierbare Unterbrechung (3 verschiedene Behandlungsmodi)

2. nichtmaskierbare Unterbrechung vorhanden vorhanden

Wartesteuerung: Refreshsteuerung:

### 2.4. Speicher

Schaltkreistypen: Q260 (U 555)

Q240 (K 505 RY2)

Kapazität: 4K Byte, bestehend aus:

- 3K Byte PROM (abrutschbar in Stufen zu 1K Byte)

- 1 K Byte stat. RAM (n-MOS) fest

#### Adressierung:

Adressen:

- 1. PROM 0000<sub>H</sub> ... 03FF<sub>H</sub>

- 2. PROM 0400<sub>H</sub> ... 07FF<sub>H</sub>

- 3. PROM 0800<sub>H</sub> ... 0BFF<sub>H</sub>

- RAM 0C00<sub>H</sub> ... 0FFF<sub>H</sub>

### 2.5. Zähler/Zeitgeber (CTC)

Schaltkreistyp: Q302 (U 555)

Anzahl der Kanäle: 4

Adressierung:

Adressen:

Ausgangssignale: 0000<sub>H</sub> ... 0031<sub>H</sub>

MOS, TTL-kompatibel (max. 1,8 mA)

Eingangssignale: MOS, TTL-kompatibel

Betriebsarten: 1. Zeitgeber

2. Zähler

VTL-5 1.12.517101.0/61

CPU, Takt, Reset, Busacken

max. Bauhöhe des Bestückungsraumes = 13,5 mm

|             |        |                                                     |        |                    |  |

|-------------|--------|-----------------------------------------------------|--------|--------------------|--|

|             |        | Reisekostenabrechnung                               |        | Mitarbeiterkennung |  |

|             |        |                                                     |        | K 2521             |  |

|             |        | Bemerkung                                           |        | 1:1                |  |

|             |        | Leiterplatte-Bestückung<br>(Zentrale Recheneinheit) |        |                    |  |

| Datum       |        | Zeitraum                                            |        |                    |  |

| 1983/7      | 16.06. | 1983/7                                              | 16.06. |                    |  |

| Bestell-Nr. |        |                                                     |        |                    |  |

| Kontrolle   |        |                                                     |        |                    |  |

| Teileanz.   |        |                                                     |        |                    |  |

| Summe       |        |                                                     |        |                    |  |

| Einz. Art.  |        | Zu-Termin                                           |        |                    |  |